PULP: An open hardware platform, the story so far

HPCA2018 Workshop and Tutorial Agenda

A workshop as part of the 24th IEEE International Symposium on High-Performance Computer Architecture (HPCA) 2018, Vienna Austria.

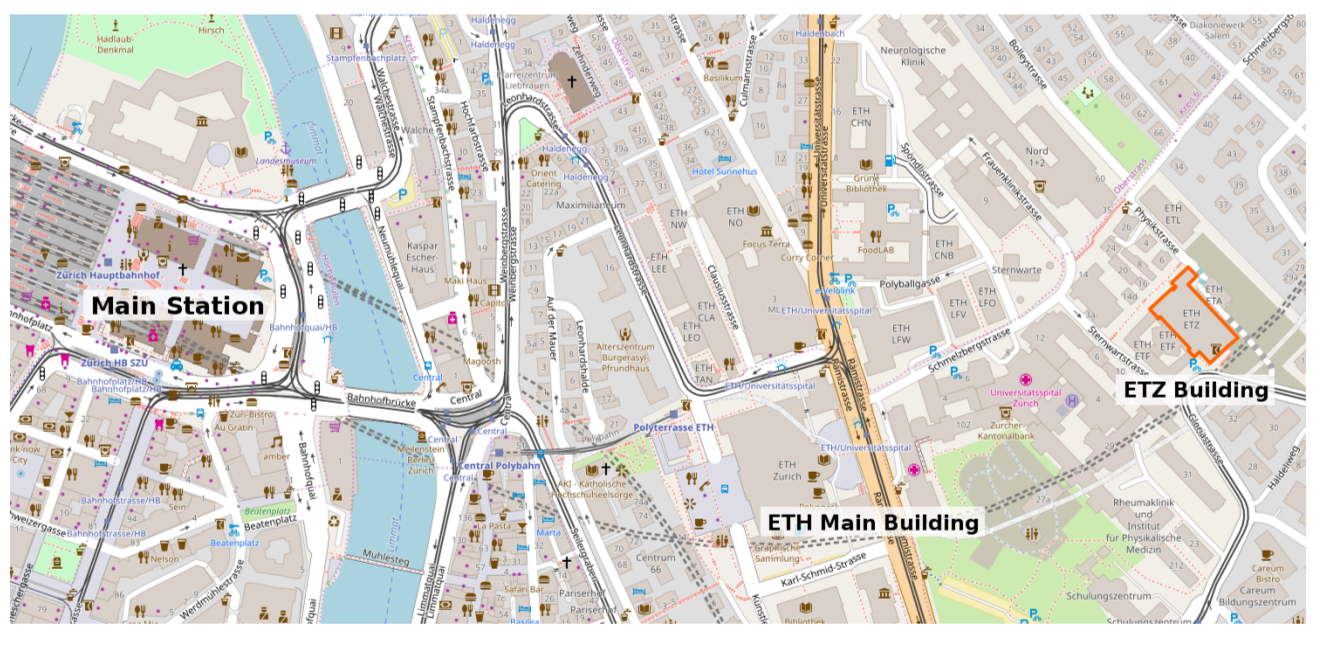

In just under 5 years the Parallel Ultra Low Power (PULP) project led by the ETH Zurich and University of Bologna has been a huge success. Indeed, it provides high-quality, silicon-proven processing platforms based on the popular RISC-V ISA, under a permissible Solderpad license to many users both in the industry and academia. In this workshop, we will present an overview of the project, describe the latest developments especially relevant to high-performance computing and have live demonstrations of all our systems.

Several senior members of the PULP team will be on hand to answer your questions and will give talks on:

– State of open source hardware

– Summary of present and future PULP platforms including our Neurostream accelerators

– Ariane: Next generation of 64-bit RISC-V implementations

– Heterogeneous Embedded Research Platform (HERO), a RISC-V based multi-cluster platform combined with an ARM Cortex-A host processor

– Our work on PULP-CAPI (Coherent Accelerator Processor Interface) allowing PULP clusters to be directly connected to HPC nodes

– Implementing novel transprecision paradigms within PULP systems, exploring different floating point formats including sub-32bit formats.

– How accelerators can be directly connected to many-core PULP systems with direct access to shared local scratchpad memories

Leave A Comment